# **Review Paper**

# New Dielectric Materials and Insulators for Microelectronic Applications

# H. Treichel, E. Eckstein W. Kernce

<sup>a</sup>Fraunhofer Institute for Solid State Technology, 80686 Munich, Germany

<sup>b</sup>Siemens Corporation, IBM Facility, Corbeil-Essonnes, France

<sup>c</sup>Werner Kern Associates, East Windsor, NJ 08520, USA

(Received 5 June 1995; accepted 21 July 1995)

Abstract: With each new generation of microelectronic devices new and more stringent demands are set for the materials being used. One can no longer rely on traditional choices but has to search for alternatives. Until recently, the oxide and nitride of silicon have been used almost exclusively for dielectric applications. Now, both low and high permittivity replacements are needed for different applications. Also, the planarity requirements for multilevel devices are driven by decreasing metal pitches and resultant limitations in photolithography. Planarization approaches, such as spin-on glass or deposition/etchback sequences, are mainly limited by their effective planarization range. Chemical–mechanical polishing (CMP) thus gains increasing importance for global planarization.

In the first part of this article we survey dielectric materials used currently with respect to their properties, applicability, processing, advantages, and limitations for ULSI (ultra large-scale integration) multilevel interconnect systems. The second part is devoted to trends and new dielectric materials thereof for microelectronic applications. © 1996 Elsevier Science Limited and Techna S.r.l.

# 1 ROLE OF DIELECTRICS IN MICROELECTRONICS

One basic function of a dielectric (strictly speaking an insulator) in a multilevel interconnect system is the electrical isolation of one level of conductor from another. The levels in which dielectrics are applied are:

- (i) premetal

- (ii) intermetal / interlevel

- (iii) above metal

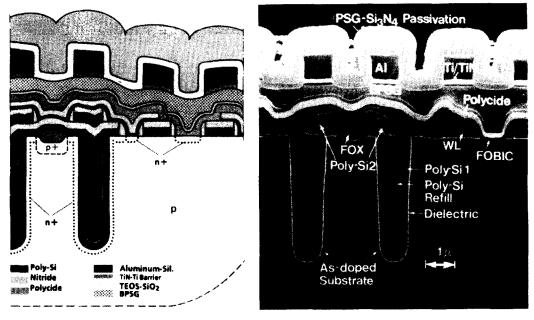

The level determines the specific use of a dielectric as etching mask, barrier layer, gate dielectric, varactor dielectric, separation of active and passive components of a device, contour tapering, planarization, passivation and more (Fig. 1, Table 1).<sup>1,2</sup>

Planarization (local or global) plays an increasingly important role in device processing because of the increasing number and complexity of layers and features in advanced ULSI silicon circuits.

#### **2 SURVEY OF MATERIALS**

Amorphous silicon dioxide was the first dielectric introduced to silicon technology about 40 years ago. However, in recent years, several limitations of  $SiO_2$  for certain applications, as well as greater demands associated with increasing integration densities, have intensified the search for alternative materials and processes.

CVD silicate glasses, such as arsenosilicate (AsSG),<sup>3-5</sup> phosphosilicate (PSG),<sup>6-8</sup> borophosphosilicate (BPSG),<sup>9,10</sup> have found wide application in MOS integrated circuits. Also, the nitrides of silicon (SiN<sub>x</sub>, SiO<sub>x</sub>N<sub>y</sub>)<sup>11,12,14</sup> and boron (BN<sub>x</sub>, SiB<sub>x</sub>N<sub>y</sub>)<sup>13,15,19</sup> and certain organic compounds, such as polyimides and Teflon<sup>®</sup>, <sup>16</sup> have their place in microelectronics (Table 2).

#### 2.1 Required properties

The more advanced an integrated circuit becomes the more stringent are the demands for certain properties of a dielectric. Table 3 lists the properties a dielectric layer must posses in order to be useful for our applications.<sup>2,17</sup>

In addition, it is essential that the dielectric maintains its specified electrical, physical and chemical properties during the device processing and after incorporation in the device structure.

## 2.2 Survey of processes

The deposition processes for dielectrics include chemical vapour deposition in its various techniques (low-pressure, atmospheric-pressure, plasmaenhanced, photo-assisted, ozone-supported), physicalchemical deposition (sputtering), spin-on techniques, and film formation processes based on reaction rather than deposition (e.g. thermal oxidation). Depending on whether the quality is determined by conformity and/or electrical properties, a specific deposition method is chosen, generally favouring those with the lowest deposition temperature. A major step towards reducing the thermal budget

Fig. 1. A cross-section through the cell-array of a 4-Mbit DRAM.

Table 1. Uses of dielectric materials

| Level                   | Application                                                                                |                                                                                                        |

|-------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Pre-metal               | dopant source<br>etching mask<br>varactor dielectric<br>gate dielectric<br>gettering layer | separation of active and passive components insulator planarization barrier layer capacitor dielectric |

| Inter-level/inter-metal | planarization<br>contour tapering<br>barrier layer                                         | insulator<br>etching mask                                                                              |

| Above metal             | planarization<br>insulator<br>passivation                                                  | barrier layer<br>etching mask<br>mechanical polishing stop                                             |

Table 2. Uses of specific materials

| Level                   | Layer application                                                                                                                        |                                                                                                                                                                                                                                                               |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pre-metal               | AsSG<br>BSG, PSG<br>SiN <sub>x</sub><br>'ONO'<br>SiO <sub>2</sub><br>SiO <sub>2</sub><br>PSG, BPSG                                       | dopant source, trench capacitor dopant source, transistor base etching mask, barrier layer varactor dielectric gate dielectric, insulator, capacitor dielectric separation of active and passive components planarization (local), insulator, impurity getter |  |

| Inter-level/inter-metal | BPSG<br>organic polymers<br>SiO <sub>2</sub><br>SiN <sub>x</sub> , SiO <sub>x</sub> N <sub>y</sub>                                       | planarization (local), contour tapering insulator, planarization (local and global) insulator, etching mask barrier layer                                                                                                                                     |  |

| Above metal             | organic polymers<br>PSG, SiO₂<br>SiN <sub>x</sub> , SiO <sub>x</sub> N <sub>y</sub><br>BN <sub>x</sub> , SiB <sub>x</sub> N <sub>y</sub> | planarization (global), insulator, enhancement of switching performance passivation protective passivation, etching mask, stops for mechanical polishing protective passivation, etching mask, stops for mechanical polishing                                 |  |

Table 3. Required properties of dielectric films

No moisture absorption/adsorption

Etchablility (wet or dry)

Permeability to hydrogen to reduce the concentration to interface states (<10<sup>11</sup> cm<sup>-2</sup>/eV)

Good barrier against alkaline ions

No residual constituents that outgas during subsequent processing

Low dielectric constant to minimize the capacitance between metal lines and to enhance switching performance

High breakdown field strength (1-10 MV/cm)

Low current leakage (<10<sup>-9</sup> A/cm<sup>2</sup>)

High surface resistivity

Cleanliness in terms of incorporation of electrical charges (<10<sup>-10</sup> cm<sup>-2</sup>) or metallic impurities (<10<sup>10</sup> at/cm<sup>2</sup>)

Low defect density including pinholes and particles (<0.02 cm<sup>-2</sup>)

High permittivity to greatly reduce cell areas

Low stress, preferably compressive

Good adhesion to underlying surfaces and of subsequently deposited layers to itself

Temperature stability

Excellent step coverage (>80%)

High uniformity across the wafer and from run to run (₹3% nonuniformity)

Manufacturability, process compatability

Planarizeability (local, global)

Table 4. Processes for forming dielectric films

| Level                     | Layer                          | Process                                  |  |

|---------------------------|--------------------------------|------------------------------------------|--|

| Pre-metal                 | AsSG                           | LPCVD                                    |  |

|                           | BSG                            | LPCVD, APCVD                             |  |

|                           | 'ONO'                          | oxidation / LPCVD                        |  |

|                           | SiO <sub>2</sub>               | LPCVD, thermal oxidation, APCVD, spin-on |  |

|                           | Si <sub>3</sub> N <sub>4</sub> | LPCVD                                    |  |

|                           | PSG, BPSG                      | LPCVD, APCVD                             |  |

| Inter-level / inter-metal | BPSG                           | PECVD, APCVD, LPCVD                      |  |

|                           | organic polymers               | plasma polymerization, CVD, spin-on      |  |

|                           | SiO <sub>2</sub>               | PECVD, LPCVD                             |  |

|                           | SiN <sub>x</sub>               | PECVD                                    |  |

| Above metal               | organic polymers               | plasma polymerization, CVD, spin-on      |  |

|                           | PSG, SiO <sub>2</sub>          | PECVD, APCVD                             |  |

|                           | SiN <sub>x</sub>               | PECVD                                    |  |

for device production is the use of plasma CVD processes. Radiation damage and incorporation of gaseous components and impurities by back-sputtering of metals from the electrodes can be minimized or eliminated by use of low-energy ECR (electron cyclotron resonance) or downstream plasma deposition (Table 4).

# 3 EXAMPLES OF CURRENTLY USED DIELECTRIC MATERIALS

#### 3.1 Pre-metal

DRAM generations up to the 64-Mbit level use either thin silicon dioxide layers or composite layers like ONO (oxide/nitride/oxide) as varactor dielectrics. These films are generated by high-temperature oxidation and deposition processes in large wafer batches. They fulfill the properties listed in Table 3, and their properties and deposition processes are well understood. Nevertheless, increasing integration densities have pushed the manufacturability of these films and their integrity to their limits. The equivalent oxide thickness is below 5 nm, close to the thickness (~3 nm) where Fowler–Nordheim tunnelling jeopardizes the insulating film properties of the compound film (Fig. 2).<sup>14</sup>

For advanced ULSI devices, materials with a higher dielectric constant are sought to replace the thin films by thicker dielectrics that can be deposited more precisely and reliably. <sup>18–20</sup> From all the materials that have been investigated, Ta<sub>2</sub>O<sub>5</sub> is the most promising candidate to date.

438 H. Treichel et al.

Fig. 2. This TEM micrograph shows an ONO film at the upper corner of a trench etched into the silicon substrate.

#### 3.2 Inter-level

After the formation of the MOS transistors the topography of the wafer has become critical, the highest points being the gate edges on top of the isolation oxide. The patterning of the levels above this topography becomes increasingly difficult for lithography (depth of focus) and pattern etching. Therefore, a planarizing step has to be included before putting down additional layers.

High-temperature CVD oxide films (deposited at 900°C by the reaction of dichlorosilane and nitrous oxide) were among the first materials for this purpose. Such films provide excellent step coverage and dielectric properties. Unfortunately, these films cannot be flowed or reflowed, because they cannot be doped at the high deposition temperature. TEOS-based films deposited at about 700°C, doped with boron and/or phosphorus, were developed consequently. Liquid organic dopant sources can replace the toxic gases silane, diborane and

phosphine. In addition, new plasma-enhanced processes allow the deposition at lower temperatures.

The flow or reflow of these films leads to local planarization over submicron areas. The planarity requirements for multilevel interconnects are driven by the demand for more levels of conductive layers with decreasing pitch and a resultant lithography depth of focus.

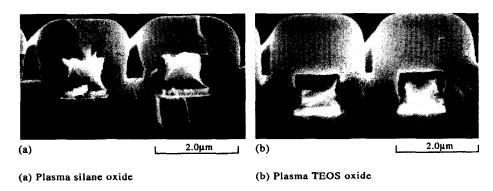

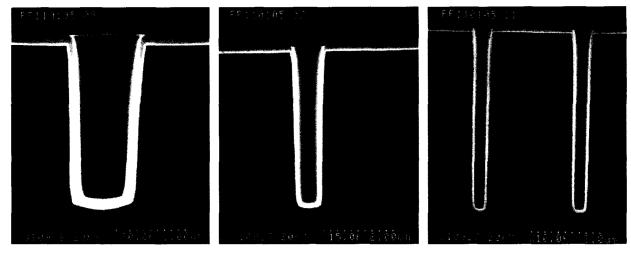

Increased aspect ratios of gate conductors and metal wiring layers make void-free gap filling more and more difficult with standard techniques. Multistep alternating deposition and etch processes, thermal CVD (ozone supported), and dual-frequency plasma deposition are currently state of the art. The conformality of the deposited layers is the limiting gap fill factor. Figure 3 illustrates the step coverage of a standard PECVD oxide and an ozone assisted TEOS oxide over patterned metal lines.<sup>21</sup>

The PECVD process displays considerable breadloafing or formation of undercut deposition pro-

Fig. 3. Comparison of the step coverage of plasma SiO<sub>2</sub> deposited from silane or TEOS as reactants. (Photographs courtesy of Novellus Systems, Inc.)

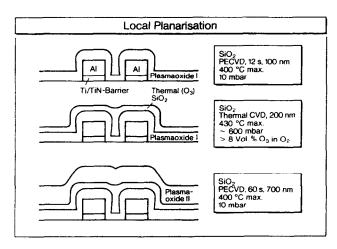

Fig. 4. Schematic diagram of ILD planarization sequence.

files on the sidewalls of the structures. If the planarization is to occur below an aluminium wiring level, flow or reflow of the doped oxide or flow glass smoothens the contours and allows local planarization. Integration of glass deposition and subsequent fusion flow into one 'flow-as-you-go' BPSG process has been demonstrated successfully by Lam Research Corporation (Integrity®).<sup>22</sup>

#### 3.3 Inter-metal/above metal

If the dielectric has to be applied between aluminium levels, thermal flow can no longer be applied because of the low melting temperature of the metal. The films can be formed by a number of processes, including atmospheric pressure, low pressure, and plasma-enhanced CVD with or without RIE etchback, by spin-on techniques, and by combinations of these processes (Fig. 4). Traditional planarization methods are limited by the planarization range of the process or process sequence used.<sup>23</sup>

In addition to the requirements of planarization, the switching performance of ULSI devices has to be improved. Thus, low dielectric constant dielectrics are needed to reduce the wiring capacitance between inter-level metals, both vertically and inplane. The most commonly used materials are spun-on polyimides with a dielectric constant of about 3 and a low degree of dielectric loss. 16 However, low resistance to higher temperature and moisture uptake of polyimides (and of organics in general) tend to limit their applications to the final stages of IC processing. Although recent efforts show promising results of integration of organic polymers as inter-metal dielectric in ultra scale integrated circuits.

# 4 NEW DIELECTRIC MATERIALS FOR MICROELECTRONIC APPLICATIONS

A selection of new materials and techniques that have been investigated for integrated circuit processing is presented in Table 5.<sup>24–32</sup>

A few examples will highlight the approaches that have been taken to steadily improve device quality and reliability with every new generation of device manufacturing.

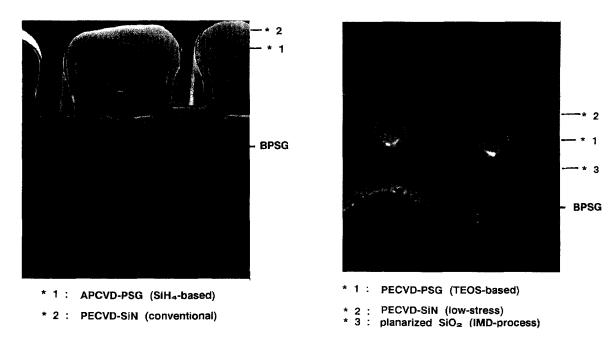

## 4.1 Tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>)

High-density DRAMs require a smaller cell area but nearly constant storage capacitance. Therefore, stacked capacitor cells<sup>32</sup> and trench capacitor cell structures, 3,6 as well as so-called fin-structures, 33 have been studied extensively. Also, several metal oxides (Ta<sub>2</sub>O<sub>5</sub>, Nb<sub>2</sub>O<sub>5</sub>, Y<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, and more) with dielectric constants ranging from 10 to 100, provide a near-term solution for future ICs like the 64-Mbit DRAM up to the 1-Gbit DRAM. 18-20 Ta<sub>2</sub>O<sub>5</sub> (Fig. 5) is the technologically most intensively investigated high dielectric constant material and is the candidate of choice for the intermediate production technology for advanced Mbit DRAMs. With this material, low leakage currents  $(<10^{-9} \text{ A/cm}^2)$ , high breakdown voltages (>7MV/ cm) and equivalent oxide thicknesses below 2 nm have been achieved. The electrode materials are titanium nitride  $(TiN_x)^{34}$  and, as the preferable choice, ruthenium oxide (RuO<sub>2</sub>).<sup>35</sup>

Table 5. Recent and new dielectrics

| Level                   | Layer                                                                    | Process                                        | Purpose                                                                                     |

|-------------------------|--------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|

| Pre-metal               | Ta <sub>2</sub> O <sub>5</sub><br>Ferroelectrics                         | CVD sputtering, CVD                            | non-volatile memories, stacked memories, varactor or gate dielectric                        |

| Inter-level/inter-metal | silicate glasses<br>BN <sub>x</sub> /SiB <sub>x</sub> N <sub>y</sub>     | CVD/CMP, PECVD                                 | planarizing insulator etch-stop/<br>CMP stop                                                |

| Above metal             | Teflon Parylenes fluorinated SiO <sub>2</sub> selective SiO <sub>2</sub> | Spin-on, low temperature reaction, thermal CVD | low dielectric constant material,<br>planarizing insulator passivation<br>protective layers |

440 H. Treichel et al.

Fig. 5. Step coverage of CVD Ta<sub>2</sub>O<sub>5</sub> in deep trenches with different aspect ratios.

## 4.2 Chemical-mechanical polishing (CMP)

This technique, derived from the polishing technology of silicon wafers, has been used to fabricate globally planarized multilevel interconnects with applications ranging from SRAMs<sup>30</sup> to multichip modules. However, structure dependence effects, such as dishing, can limit the planarity attainable with CMP.<sup>32</sup> In addition, high polish-selectivity is mandatory to obtain the required uniformity of the polishing process and to improve manufacturability. Thus, new processes have been developed to alleviate structure dependency and to introduce insulating polish stop layers, such as boron nitride or silicon boron nitride. 13,29 The ability to stop the polishing process when planarity is reached is a critical feature for the manufacturability of CMP. Improved processing can be achieved by an endpoint detection or by use of a stop layer. To be most effective, this stop layer must have a significantly lower removal rate than that of the layer to be polished. Silicon nitride, boron nitride and silicon boron nitride have been proven to be excellent stop layers. The deposition processes for such films have been described elsewhere. 13 Table 6 lists the selectivities obtainable with  $BN_x$  or  $SiB_xN_y$  for a particular type of polishing slurry.

Table 6.

| CMP of:                        | Selectivity to: |                 |  |

|--------------------------------|-----------------|-----------------|--|

|                                | Boron nitride   | Silicon nitride |  |

| Silicon oxide SiO <sub>2</sub> | 30:1            | 6:1             |  |

| Poly silicon                   | 500:1           | 280:1           |  |

| Tungsten                       | 150:1           | 75:1            |  |

| Aluminium                      | 40:1            | 40:1            |  |

The data clearly show that  $\mathrm{BN}_x$  provides a significantly better CMP stop than silicon nitride.

## 4.3 Teflon®

As a low permittivity material, Teflon offers an excellent choice with its low dielectric constant of  $\epsilon \sim 1.9$ . This low constant should greatly reduce crosstalk capacitance and propagation delay in metal interconnects, making this material most desirable for incorporation into multilevel devices; it definitively has the desired properties for high-speed applications.

However, among the problems connected with applying Teflon are its low decomposition temperature ( $\sim 300^{\circ}$ C), its low friction coefficient, and the technique for its formation manufacturably. Several approaches have been investigated (e.g. at the University of California, Berkeley, at Air Products, and at Siemens AG, Germany) to address the problems connected with this potentially useful material. Spin-on techniques with dissolved Teflon and plasma polymerization of  $CH_2F_2$  or  $CF_6$  have been developed; further heat treatments to provide a desirable 'sticky' surface are under investigation.

#### 4.4 Planarized passivation

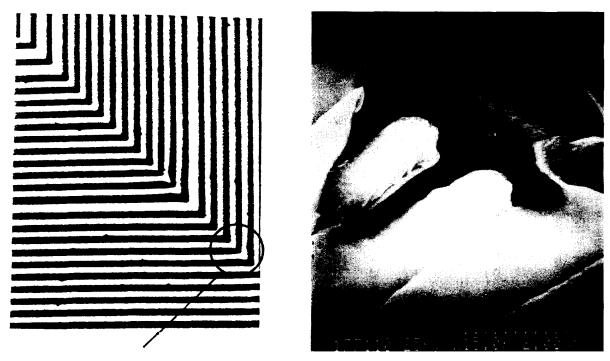

Most of the current technologies for the passivation of ULSI devices do not take into account the geometric dimensions of the peripheral regions of the ICs. Further, because of a larger distance between conductor lines at rectangular corners (Fig. 6) it is not possible to provide a void free passivation layer over the metal lines. Consequently, standard plasma-etching and/or wet etch patterning lead to exposure of the lines to the environment or packaging material, possibly causing corrosion and failure of the devices.<sup>36</sup>

Applying standard dep/etch sequences in combination with conventional passivation techniques, it was shown using a 4-Mbit DRAM (Fig. 7) and a

Fig. 6. "Optical distortions" in device corners and holes in passivation layer after conventional device patterning.

Fig. 7. SEM cross-section of a 4-Mbit DRAM illustrates the smooth surface achieved after planarized passivation compared with the conventional technique.

double-layer logic device that the proposed novel planarized passivation provides the following advantages:

- void-free planarization of a wide range of aspect ratios (>1)

- absence of holes in the passivation layer

- no encapsulation of by-products

- no degradation of electrical device parameters

- drastic increase in device production yield

## **5 SUMMARY**

In the first part of this article we surveyed currently used dielectric materials with respect to their properties, applicability, processing, advantages, and limitations for ULSI multilevel interconnect systems. The second part was devoted to trends and new dielectric materials for microelectronic applications. Some examples of new approaches for overcoming device production drawbacks

and for improving performance have been presented.

#### **ACKNOWLEDGEMENTS**

The authors wish to express their gratitude to their coworkers at the IBM and Siemens facilities, as well as to their friends and colleagues who offered their constructive criticism of this article.

#### REFERENCES

- 1. TREICHEL, H., MITWALSKY, A., SANDLER, N. P., TRIBULA, D., KERN, W. & LANE, A. P., Adv. Mat. for Optics and Electronics, 1 (1992) 299.

- HIEBER, K., KÖRNER, H. & TREICHEL, H., Thin Solid Films, 181 (1989) 75.

- BECKER, F. S., TREICHEL, H., RÖHL, S. & PAWLIK, D., Abstract number 366, ECS Ext. Abstr., 86-2 (1986) 396.

- BECKER, F. S., TREICHEL, H. & RÖHL, S., J. Electrochem. Soc., 136 (1989) 3033.

- BECKER, F. S. & TREICHEL, H., In Proc. 6th European Conf. on CVD, ed. R. Porat. Israel, 1987, p. 207.

- BECKER, F. S. & RÖHL, S., J. Electrochem. Soc., 134 (1987) 2923.

TREICHEL, H., TOMKEWITSCH, J. V. & SPIND-

- TREICHEL, H., TOMKEWITSCH, J. V. & SPIND-LER, O., In *Plasma Processing of Materials*, ed. J. J. Pouch & S. A. Alterovitz. Mater. Sci. Forum, Trans. Tech. Publ., Switzerland, 1993, p. 359.

- TREICHEL, H., BRAUN, R., GABRIC, Z., SPINDLER, O. & GSCHWANDTNER, A., J. de Physique II, 1 (1991) 839.

- 9. TREICHEL, H., SPINDLER, O., BRAUN, R., BROOKS, T. A. & NOWAK, R., In *Proc. 8th Symp. on Plasma Processing*, ed. G. S. Mathad & D. W Hess. The Electrochemical Soc. Inc., Pennington, NJ, 1990, PV 90-14, p. 574.

- BECKER, F. S., PAWLIK, D., SCHÄFER, H. & STAUDIGL, G., J. Vac. Sci Technol., B4 (1986) 832.

- 11. CHU, T. L., J. Vac. Sci. Technol., 6 (1969) 25

- BANERJEE, S., SHEN, B., CHEN, I., BOHLMAN, J., BROWN, G. & DOERING, A., J. Appl. Phys., G5(3) (1989) 1140.

- 13. NGUYEN, S. V., NGUYEN, T., TREICHEL, H. & SPINDLER, O., In *Proc. of the 11th Int. Symp. on Plasma Chem.*, ed. J. Harry, **3** (1993) 981.

- MÜHLHOFF, H. M. & McCAUGHAN, D. V., In Handbook on Semiconductors, Device Physics, Vol. 4, Chap. 3, ed. T. S. Moss & C. Hilsum. Elsevier Science Publishers, 1993.

- MAEDA, M., MAKINO, T., YAMAMOTO, E. & KONAKA, S., IEEE Trans. Electr. Dev., 36 (1989) 1610.

- HARROP, P. J. & CAMPBELL, D. S., Thin Solid Films,

2 (1968) 273.

- 17. KERN, W., Tutorial Booklet, 10th VMIC Conf., Santa Clara, CA, 1993.

- 18. TREICHEL, H., MITWALSKY, A., SANDLER, N. P., TRIBULA, D., KERN, W. & LANE, A. P., In Korean Technical Trade Mission, Semicon, Korea, 1992.

- TREICHEL, H., MITWALSKY, A., ZORN, G., TEMPEL, G., KERN, W., SANDLER, N. P. & LANE, A. P., MRS Symp. Proc., 282 (1992) 557.

- TREICHEL, H., MITWALSKY, A., TEMPEL, G., ZORN, G., BOHLING, D. A., COYLE, K. R., FELKER, B. S., GEORGE, M., KERN, W., LANE, A. P. & SANDLER, N. P., Abstract number 156, ECS Ext. Abstr., 93-2 (1993) 250.

- STAMPER, A. K., McDEVITT, T. L., PENNINGTON, S. L., LUCE, S. F. & SOTO, A. B., In *Proc. 10th VMIC Conf.*, Santa Clara, USA. IEEE, 1993, p. 160.

- JENSEN, K. F. & KERN, W., In Thin Film Processes II, ed. J. L. Vossen & W. Kern, Chap. III-1. Academic Press, New York, 1991, p. 283.

- SPINDLER, O. & NEUREITHER, B., Thin Solid Films, 175 (1989) 67.

- CARRANO, J. C., SUDHAMA, J. H., TASCH, A. F. & MILLER, W., *IEDM Tech. Digest*, (1989) 225.

- 25. MOAZZAMI, R., HU, C. & SHEPHERD, W. H., *IEDM Tech. Digest*, (1990) 417.

- ITOH, H., KASHIHARA, K., OKUDAIRA, T., TAKAMOTO, K. & AKASAKA, Y., IEDM Tech. Digest, (1991) 477.

- KOYAMA, K., SAKUMA, T., YAMAMICHI, S., WATANABE, H., AOKI, H., OKYA, S., MIYASAKA, Y. & KIKKAWA, T., IEDM Tech. Digest, (1991) 823.

- 28. HOMMA, T. & MURAO, Y., IEDM Tech. Digest, (1991) 289.

- POON, S., GELATOS, A., PEERERA, A. H. & HOFMANN, M., 1993 VLSI Techn. Symp., Ext. Abstract no. 8, B-5, 1993, p. 115.

- 30. UTTECHT, R. R. & GEFFKEN, R. M., In Proc. 9th VMIC Conf., Santa Clara, USA. IEEE, 1991, p. 20.

- NGUYEN, S. V., DOBUZINSKY, D. & HARMON, D., Solid State Technol., 10 (1990) 73.

- TAKEMAE Y., IEEE Solid State Silicon Circuits Conf., Digest of Tech. Papers. 1985, p. 250.

- Digest of Tech. Papers, 1985, p. 250.

33. EMA, T., KAWANAGO, S., NISHI, T., YOSHIDA, S., NISHIBE, H., YABU, T., KODAMA, Y., NAKANO, T. & TAGUCHI, M., IEDM Tech. Digest, (1988) 592.

- 34. KOMIJAMA, S., SAEKI, T., MOI, K. & NUMASAWA, Y., IEDM Tech. Digest, (1991) 827.

- SANDLER, N. P., Lam Research Corp., private communications.

- 36. MENZ, K. D., BRAUN, R., HENKEL, W., HUBER, R., NEUREITHER, B., SPINDLER, O. & TREICHEL, H., In *Proc. 7th VMIC Conf.*, Santa Clara, USA. IEEE, 1990, p. 384.